EVALUATION EN ARCHITECTURE DES ORDINATEURS TEST 01/ XX

EXERCICE 01 : 5pts

En utilisant un codage sur 5 bits, donner l’équivalent binaire des valeurs décimales suivantes, pour chacun des trois codes étudiés (Valeur Absolue Sans Signe,Valeur Absolue plus Signe, Complément à 2) Complétez le tableau suivant :

|

Nombre décimal

|

Valeur Absolue

|

Signe + valeur Absolue

|

Complément a 2

|

|

|

|

00111

|

|

|

|

|

01001

|

|

|

13

|

|

|

|

|

-7

|

|

|

|

|

|

|

11001

|

|

Exercice 02 : 5pts

- Convertissez les valeurs suivantes (représentées en décimal) en standard IEEE 754 Simple précision. Donner le résultat en binaire. 1pts

a) 128 , b) -32,75

- Donner les intervalles de codage d’un entier naturel sur : 8 bits et 16 bits 1pts

- Effectuer en binaire les opérations 13 -5 et 5 –13. (Complément a deux) 1pts

- Donnez le Codage de (9,375)10 en base deux avec une précision de 2-3 (3 chiffres après la virgule) 1pts

- Donnez la représentation de : (25)10 = ( ? )Gray , (90)10=( ?)DCB 1pts

Exercice 03 : 5pts

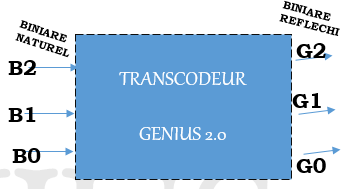

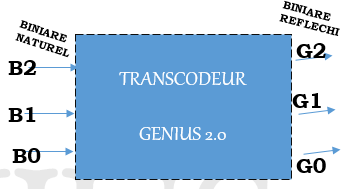

Les étudiants du GROUPE GENIUS souhaites développez un circuit logique (transcodeur) muni de 3 variables d’entrée (B2,B1,B0)2 représentant le nombre N dans le code binaire naturel (ou pur), et qui donne en sortie (G2, G1, G0) représentant le même nombre dans le code Gray (ou binaire réfléchi).

1) Dresser une table de vérité traduisant le fonctionnement,

2) A l’aide du tableau de Karnaugh, trouver les équations des sorties : G2, G1 et G0,

3) Dessiner le logigramme avec uniquement des portes “XOR” à deux entrées,

4) En déduire le logigramme si le code d’entrée est sur 4 bits.

5) Vérifier que ce transcodeur peut réaliser le transcodage inverse

Exercice 04 : 5pts

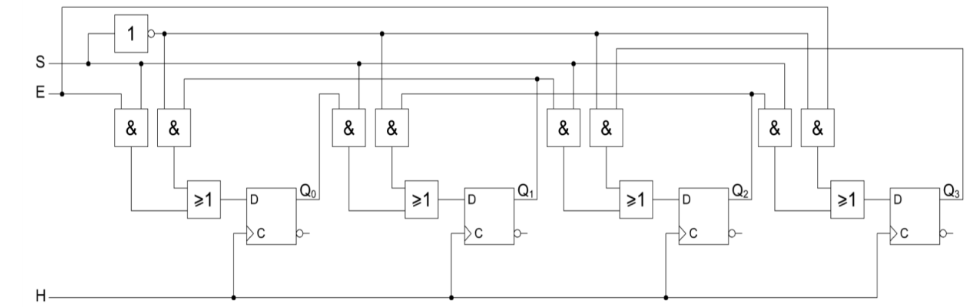

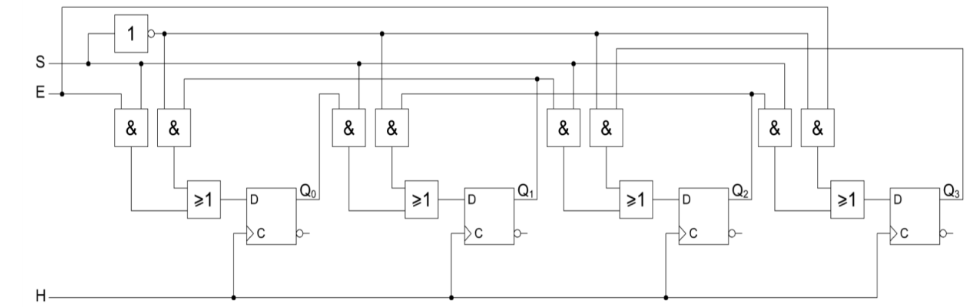

Soit le circuit séquentiel synchrone compose des Bascules D suivant :

- Donnez la table de vérité de la bascule D. 0.5 pts

- Cette bascule est-elle sensible sur niveau ou sur front ? justifier votre réponse. 1.pts

- Donnez les équations de sorties Qi des Bascules Di de notre circuit lorsque E=0 et S=0 ensuite lorsque E=1 et S=1. Expliquez le fonctionnement de ce circuit. 2.pts

- Le multiplexeur permet de sélectionner une variable logique choisie parmi 2n variables logique. C’est pour cette raison qu’il est aussi appelé sélecteur de données. L’aiguillage de l’entrée de données qui nous intéresse sur la sortie est commandé par des entrées de sélection appelées des entrées d’adresse. Donner la table de vérité d’un multiplexeur 1 parmi 4 et sa fonction logique ainsi que son schéma logique avec et sans boite noire. Donnez les applications du Mux et du Demux. 2.pts