EXERCICE ELECTRONIQUE NUMERIQUE : DEMI ADDITIONNEUR/SOUSTRACTEUR & ADDITIONNEUR/SOUSTRACTEUR COMPLET

Exercice Architecture des Ordinateurs : Demi Additionneur/Soustracteur - Additionneur/Soustracteur

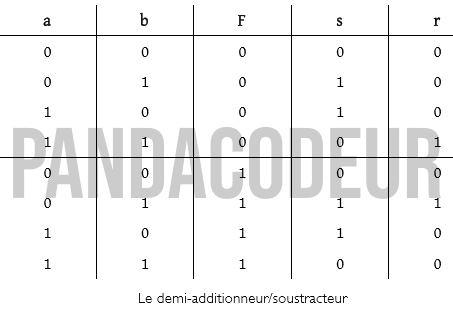

L'UAL (Unité d'Arithmétique et de Logique) est l'élément de base d'un microprocesseur. Comme son nom l'indique, son rôle est la réalisation d'opérations arithmétiques (additions, soustractions...), logiques (OR, AND, NOR...), mais aussi de décalage, et de transfert. On construit un circuit qui a deux entrées (x et y) et deux sorties (s et r) et une ligne de commande F tel que : Si F = 0, le circuit effectue une addition (x + y avec une sortie s et une retenue r) ; Si F = 1, le circuit effectue une soustraction (x – y avec une sortie s et une retenue r).

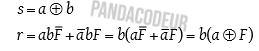

1) Donnez la table de vérité de ce circuit demi-additionneur/soustracteur. Montrez que s se calcule facilement avec une porte et r avec deux.

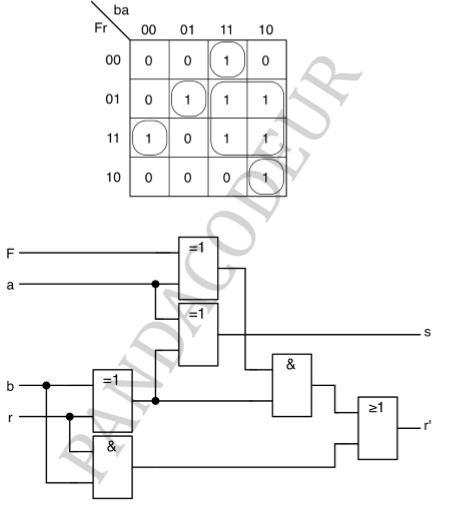

2) On construit maintenant un additionneur/soustracteur complet, c’est-à-dire un circuit à trois entrées (x, y et r), deux sorties (s et r’) et une ligne de commande F tel que : Si F = 0, le circuit effectue une addition (x + y + r avec une sortie s et une retenue r’) ; Si F = 1, le circuit effectue une soustraction (x – (y + r) avec une sortie s et une retenue r’).

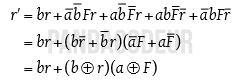

Écrivez la table de vérité de s pour la soustraction et comparez-la à celle de l’additionneur complet. Donnez l’expression logique de s. Écrivez la table de Karnaugh ainsi qu’une expression logique de r’.

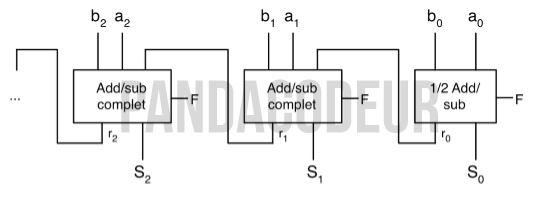

3) À partir des deux circuits précédents, proposez une construction pour un additionneur/soustracteur sur n bits, c’est-à-dire un circuit avec deux fois n bits en entrée et qui effectue l’addition ou la soustraction de ces deux nombres suivant la valeur d’une ligne de commande.